- 導入事例

- [Neat Bar/Board導入事例]東洋鋼鈑様

- 【Box導入事例】秋田大学様

- 【ECCL導入事例】大正大学様

- 【S-iDC バックアップサービス with Wasabi導入事例】春日井市民病院様

- 【工場ネットワーク導入事例】株式会社資生堂様

- 【オフィス移転事例】オートモーティブエナジーサプライ様

- 【オフィス移転事例】外為どっとコム様

- 【オフィス移転事例】GSユアサ様

- 【オフィスリニューアル事例】JR東日本ビルテック株式会社様

- 【オフィス移転事例】日本食研ホールディングス様

- 【オフィス移転事例】株式会社スコープ様

- 【オフィス移転事例】スカパーJSAT株式会社様

- 【ネットワーク導入事例】東京ステーションホテル様

- 【コミュニケーション改革事例】豊田通商株式会社様

サイト内の現在位置

DIGITAL PATH TESTERⅡ 1012A 【2019年9月 販売終了】

特長

- 豊富なレガシーインタフェース

・デジパスモード

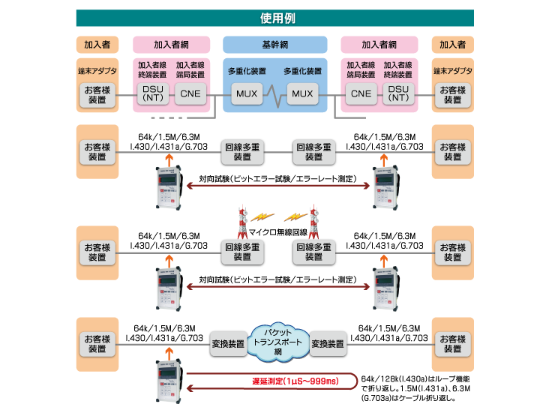

デジタルハイアラーキの0次群(64k G.703)、1次群(1.5M G.703)、2次群インタフェース(6.3M G.703)の測定が可能です。また、フレームあり/なしを選択することが可能です。

・BRIモード

64k、128kbit/s高速デジタル専用線の基本ユーザ網インタフェース(I.430またはI.430a)の測定が可能です。

・I.431aモード

1.5Mbit/s高速デジタル専用線の1次群ユーザ網インタフェース(I.431a)の測定が可能です。

・G.703aモード

6.3Mbit/s高速デジタル専用線の2次群ユーザ網インタフェース(G.703a)の測定が可能です。 - ビットエラー試験

・測定結果はエラー数/エラーレートで表示

・測定範囲はTS(タイムスロット)単位で設定

・疑似エラー、疑似警報を発出可能

(注)本ページでは「ビットエラー試験」と呼称しています。誤り率試験、ビット誤り試験、BER測定等のことです。 - 遅延測定

・往復遅延を測定し、1μs~999msの範囲で表示(現在値/最大値/最小値/平均値) - ループ(折り返し)測定

・対向のビットエラー試験信号、遅延測定試験信号を受信後、折り返して送信 - TS(タイムスロット)単位での測定が可能

- 警報・状態表示

・検出した警報や動作状態をリアルタイムに画面上で確認可能 - 外部クロック入力

・64K+8K複合バイポーラ信号に従属させ、網同期に対応した測定が可能 - 持ち運びに便利なハンディタイプ 寸法:110(W)×200(H)×45(D)mm

- ボタン操作による簡単設定

- 電源は乾電池(単3×4)またはACアダプタ

使用例

カタログダウンロード

※記載されている会社名、サービス名、商品名は、各社の商標または登録商標です。

カタログ(PDF:984KB)をダウンロード

カタログ(PDF:984KB)をダウンロード